中国移动研究院“面向存算一体芯片的模型编排算法”论文被国际神经信息处理大会录用

中国移动研究院“面向存算一体芯片的模型编排算法”论文被国际神经信息处理大会录用

近日,中国移动研究院撰写的论文“Efficient Automatic Arrangement Algorithm for Computing In Memory Chips Array”被第三十一届国际神经信息处理大会(ICONIP2024)录用。

近年来,人工智能尤其是大模型对算力的需求呈爆炸式增长,而经典的冯·诺依曼架构因存储与计算分离带来的数据搬运时延及能耗成为算力增长的主要瓶颈。存算一体技术在存储原位实现计算功能,可以突破冯·诺依曼架构瓶颈,大幅提升算力和能效水平。但是,由于存算一体芯片涉及架构、器件、材料、算法的全新创新,面临模型编排复杂度高、阵列利用率低下的问题,阻碍存算一体芯片的应用拓展。针对上述问题,论文提出一种面向存算一体芯片的新型多阵列AI模型编排算法,可以大幅提升编排效率和芯片阵列利用率。该成果为面向存算一体芯片的AI模型编排部署提供重要参考,对于推进存算一体芯片的工程化和产业化有重要意义。

图1 论文首页

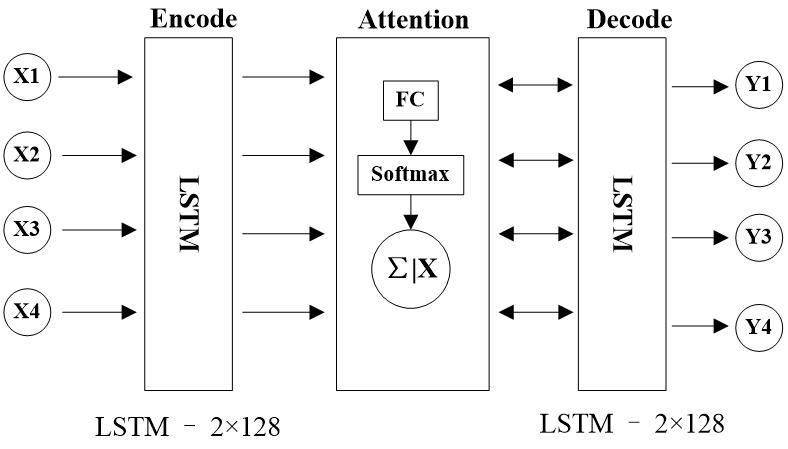

论文将AI模型不同层权重在存算一体芯片多阵列的优化编排问题转化为面向阵列利用率提升的序列到序列排序问题,创新地提出了一种基于改进指针网络(Pointer Net)的AI模型分层排序算法,采用长短期记忆网络(LSTM)作为指针网络的编码器(Encode)与解码器(Decode),增加了模型序列记忆能力,同时引入注意力机制,提升算法序列预测的准确性。图2为算法网络结构图,输入数据为模型各层权重尺寸与存算阵列尺寸的比例,输出数据为模型该层权重在阵列中的编排顺序。

图2. 基于序列到序列指针网络的AI模型分层排序算法结构图

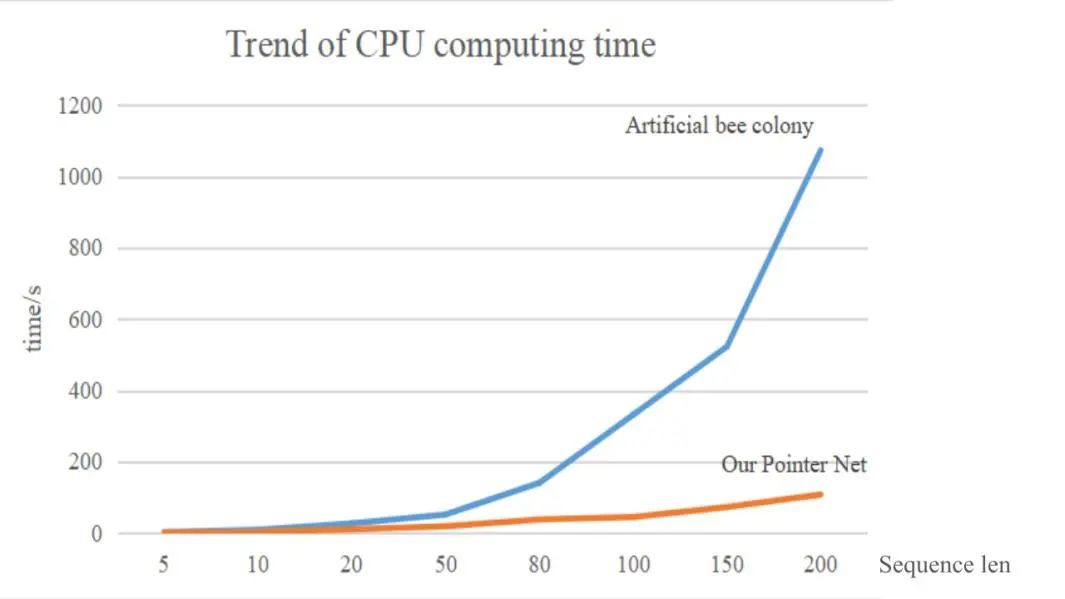

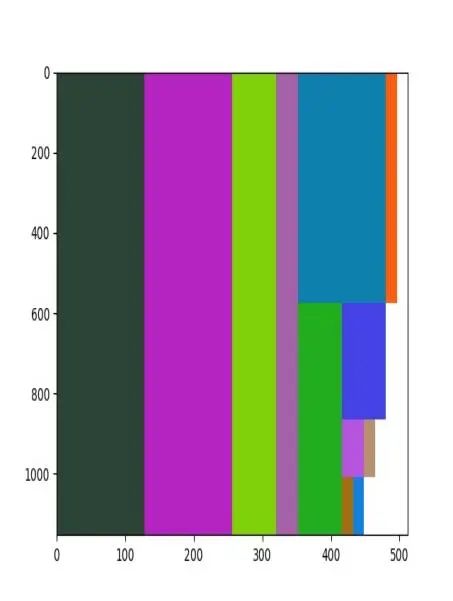

论文采用人工蜂群算法(Artifical Bee Colony,ABC)在ONNX开源模型库搜索匹配不同存算一体芯片阵列特征的网络计算层最优排序,作为标注数据集训练指针网络训练。在模型编排阶段,论文提出的基于序列到序列的模型编排算法计算复杂度由ABC算法O(n3)降为O(n),其中n为AI模型的层数,预测准确率达到ABC算法的96%,在保证准确率的同时大幅降低计算时延。尤其对于层数较多的复杂AI模型,本文方法发挥的优势更为明显,如图3所示,对于100层以上网络,编排效率超过传统ABC算法10倍。

图3. 论文算法跟人工蜂群算法计算时延对比图

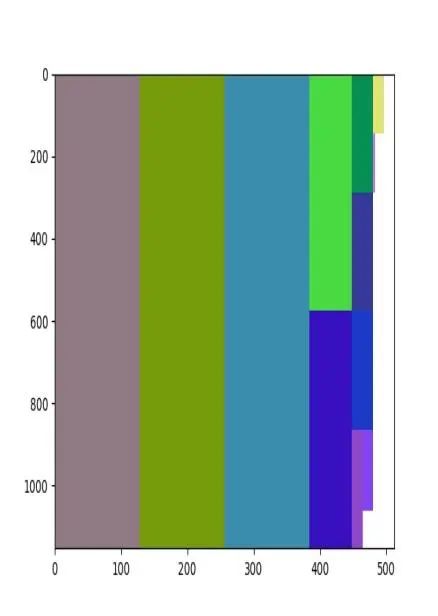

最后,基于指针网络输出地分层编排顺序,综合AI算子特征和阵列冗余空间形成算子在阵列的最优编排策略,有效保证芯片阵列占用率。图4是Yolov5s模型在一个2阵列(阵列尺寸1024x512)存算一体芯片上的编排结果,阵列1利用率达94.14%,阵列2达利用率93.97%。

图4. Yolov5s网络模型在存算一体芯片上的编排结果

下一步,中国移动研究院将继续开展存算一体关键技术研究,围绕软件架构、优化算法、场景应用等环节持续发力,推动存算一体技术成熟。

微信扫描二维码

发表您的评论吧

相关阅读

-

中国移动浙江公司全力抗击台风“康妮”保障通信畅通

分类推荐 2024-11-01 19:50:01

-

“上车即入院” 移动5G助力智慧急救跑出“加速度”

分类推荐 2024-10-28 10:33:01

-

华为杨超斌:5G-A释放移动AI无限潜能

分类推荐 2024-10-31 21:43:01

-

中国移动携手中兴通讯完成SPN 400G 现网验证

分类推荐 2024-11-15 17:54:01

-

湖北移动5G-A筑“长江新链”,全球首个内河航运通感一体预商用组网测试圆满完成

分类推荐 2024-11-01 11:26:00

-

广东联通携手贝锐、华为联合创新,打造网络智能新体验

分类推荐 2024-11-01 21:15:01

-

陕西移动携手华为融合视频,创新商用电视平台双活双中心业务

分类推荐 2024-11-01 17:53:01

-

穿越千山万水,覆盖千家万户 浙江移动全力护航“信号升格”行动

分类推荐 2024-11-08 14:32:01

-

国云基座 安全智警,中国电信共建AI+安防新未来

分类推荐 2024-10-26 11:31:00

-

“低空经济+”不断延伸!无锡移动5G-A赋能无锡新质生产力

分类推荐 2024-10-26 17:44:01

-

第二届“华彩杯”算力大赛结果揭晓,浙江移动斩获10项大奖

分类推荐 2024-11-01 18:41:00

-

珠海联通以5G科技引领,赋能珠海市海洋经济发展

分类推荐 2024-10-28 11:07:01

-

信科移动荣获“中国上市公司新质生产力50强”

分类推荐 2024-10-25 10:29:01

-

连云港海州移动“千里眼”业务助力校园安全管理

分类推荐 2024-10-26 11:23:01

-

珠海联通保障航展应急救援综合演练顺利开展

分类推荐 2024-10-28 11:05:01